# 10MHz 到 80MHz、10:1 LVDS 并串转换器(串化器)/ 串并转换器(解串器)

#### 产品简述

MS1023 串化器和 MS1224 解串器是一对 10bit 并串/串并转换芯片,用于在 LVDS 差分底板上传输和接收 10MHz 至 80MHz 的并行字速率的串行数据。起始/停止位加载后,转换为负载编码输出,串行数据速率介于 120Mbps 至 960Mbps。

上电时,这一对芯片可通过内部产生的 SYNC 样本信号同步模式进行初始化或者解串器与随机数据同步。通过使用同步模式,解串器可在特定的、更短的时间参数内建立锁定。

当没有数据传输要求时,芯片可以进入掉电模式。另外,可以通过设置输出脚为高阻态以避免 PLL 失锁。

MS1023 和 MS1224 的工作温度范围为-40°C 至 85°C。

### 主要特点

- 100Mbps 至 800Mbps 串行 LVDS 数据有效负载带宽在 10MHz 至 80MHz 的系统时钟之间

- 在80MHz 输入时,芯片功耗小于550mW(典型值)

- 使用同步模式,可快速锁定时钟

- 锁定指示器

- 不需要外部单元提供 PLL

- SSOP28 封装

- 可编程时钟边沿触发

- 流向行引脚排序,易于 PCB 版图布局

#### 应用

- 无线基站

- 底板互连

- 数字用户线接入复用器

#### 产品规格分类

| 产品     | 封装形式   | 丝印名称   |

|--------|--------|--------|

| MS1023 | SSOP28 | MS1023 |

| MS1224 | SSOP28 | MS1224 |

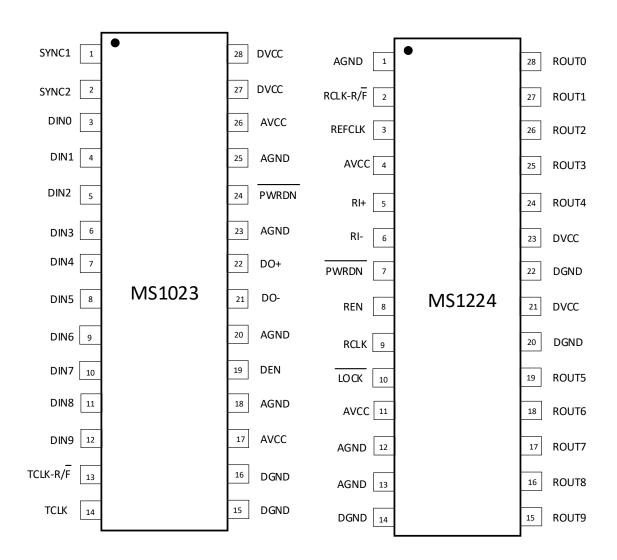

## 管脚图

# 管脚说明

| 管脚编号            | 管脚名称          | 管脚属性 | 管脚描述                                                                                                                               |

|-----------------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| El Well-Allid 3 | D 75-4, D 454 |      | MS1023                                                                                                                             |

| 1,2             | SYNC1, SYNC2  | I    | SYNC1 和 SYNC2 是或关系的 LVTTL 逻辑输入。当至少一个脚被置高长达 6 个 TCLK 周期,串化器将至少 1026 个 SYNC 样本的传输过程进行初始化。如果 1026 个 SYNC 样本发送完成后,SYNC 继续为高,那么数据传输会一直继 |

|                 |               |      | 续直到 SYNC 为低。当 SYNC 保持超过 6 个周期时,将会再次发送 1026 个 SYNC 样本。                                                                              |

| 3-12            | DINO-DIN9     | I    | 并行 LVTTL 数字输入                                                                                                                      |

| 13              | TCLK_R/F      | ı    | LVTTL 逻辑输入。低时,选择忽略 TCLK 的下降沿数据;<br>高时,选择忽略 TCLK 上升沿数据。                                                                             |

| 14              | TCLK          | ı    | LVTTL 电平参考时钟输入。MS1023 可接收 10MHz 至 80MHz 时钟。TCLK 忽略并行数据到输入锁存,同时为 PLL 提供参考频率。                                                        |

| 15,16           | DGND          | -    | 数字电路地                                                                                                                              |

| 17,26           | AVCC          | -    | 模拟电路电源(用于 PLL 和模拟电路)                                                                                                               |

| 18,20,23,25     | AGND          | -    | 模拟电路地(用于 PLL 和模拟电路)                                                                                                                |

| 19              | DEN           | I    | LVTTL 逻辑输入。低时,LVDS 串行输出处于高阻状态;<br>高时,使能串行数据输出                                                                                      |

| 21              | DO-           | 0    | LVDS 差分输出反向端                                                                                                                       |

| 22              | DO+           | 0    | LVDS 差分输出正向端                                                                                                                       |

| 24              | PWRDN         | I    | LVTTL 逻辑输入。低时,会关掉 PLL 并输出高阻态,芯片进入低功耗模式。                                                                                            |

| 27,28           | DVCC          | -    | 数字电路电源                                                                                                                             |

| 管脚编号        | 管脚名称        | 管脚属性 | 管脚描述                                                                             |

|-------------|-------------|------|----------------------------------------------------------------------------------|

|             |             |      | MS1224                                                                           |

| 1,12,13     | AGND        | -    | 模拟电路地(用于 PLL 和模拟电路)                                                              |

| 2           | RCLK_R/F    | I    | LVTTL 逻辑输入。低时,选择忽略 RCLK 下降沿数据;高时,选择忽略 RCLK 上升沿数据                                 |

| 3           | REFCLK      | I    | LVTTL 输入,为 PLL 提供 REFCLK 信号                                                      |

| 4,11        | AVCC        | -    | 模拟电路电源(用于 PLL 和模拟电路)                                                             |

| 5           | RI+         | I    | 串行数据输入,正向 LVDS 差分输入                                                              |

| 6           | RI-         | I    | 串行数据输入,反向 LVDS 差分输入                                                              |

| 7           | PWRDN       | I    | LVTTL 逻辑输入。低时,关掉 PLL 并输出高阻态,芯片进入低功耗模式。为了进入掉电模式,此脚置低至少16ns。只要 PWRDN为低,芯片就将进入掉电模式。 |

| 8           | REN         | I    | LVTTL 逻辑输入。<br>低时,ROUTO-ROUT9 和 RCLK 进入高阻态                                       |

| 9           | RCLK        |      | LVTTL 输出恢复时钟,RCLK 可忽略 Routx                                                      |

| 10          | LOCK        | 0    | LVTTL 输出。当解串器的 PLL 锁定到内嵌时钟边沿,————————————————————————————————————                |

| 14,20,22    | DGND        | -    | 数字电路地                                                                            |

| 28-24,19-15 | ROUTO-ROUT9 | 0    | 并行 LVTTL 数据输出                                                                    |

| 21,23       | DVCC        | -    | 数字电路电源                                                                           |

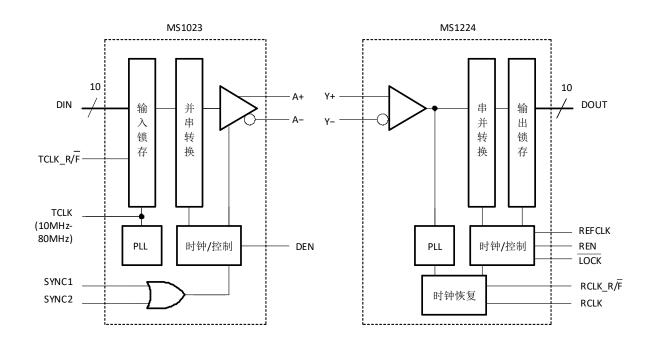

# 内部框图

### 极限参数

芯片使用中,任何超过极限参数的应用方式会对器件造成永久的损坏,芯片长时间处于极限工作 状态可能会影响器件的可靠性。极限参数只是由一系列极端测试得出,并不代表芯片可以正常工作在 此极限条件下。

| 参数                           | 符号   | <br>  额定值                   | 单位    |

|------------------------------|------|-----------------------------|-------|

| 多奴                           | 11 7 |                             | 十四    |

| Vcc                          |      | -3.0 ~ 4.0                  | V     |

| LVTTL 输入电压                   |      | -0.3 ~ V <sub>CC</sub> +0.3 | V     |

| LVTTL 输出电压                   |      | -0.3 ~ V <sub>CC</sub> +0.3 | V     |

| LVDS 接收输入电压                  |      | -0.3 ~ 3.9                  | V     |

| LVDS 驱动输出电压                  |      | -0.3 ~ 3.9                  | V     |

| LVDS 输出短路持续时间                |      | 10                          | ms    |

| ESD(HBM)                     |      | 6k                          | V     |

| ESD(MM)                      |      | 200                         | V     |

| 结温                           |      | 150                         | °C    |

| 存储温度                         | Tstg | -65 ~ 150                   | °C    |

| 最大功耗(T <sub>A</sub> =25°C)   |      | 1.27                        | W     |

| 功耗温度特性(T <sub>A</sub> =25°C) |      | 10.3                        | mW/°C |

## 推荐工作条件

|          |                |                    | )/ /) |                          |                  |

|----------|----------------|--------------------|-------|--------------------------|------------------|

| 参数       | 符号             | 最小                 | 标准    | 最大                       | 单位               |

| 电源电压     | Vcc            | 3                  | 3.3   | 3.6                      | V                |

| 接收输入电压范围 |                | 0                  |       | 2.4                      | V                |

| 接收输入共模范围 | $V_{CM}$       | V <sub>ID</sub> /2 |       | 2.4-(V <sub>ID</sub> /2) |                  |

| 电源噪声电压   |                |                    |       | 100                      | mV <sub>PP</sub> |

| 工作温度     | T <sub>A</sub> | -40                | 25    | 85                       | °C               |

# 电气参数

| 参数                     | 符号              | 测试条件                                                      | 最小值  | 典型值   | 最大值             | 单位 |  |  |  |  |

|------------------------|-----------------|-----------------------------------------------------------|------|-------|-----------------|----|--|--|--|--|

| MS1023 LVCMOS/LVTTL DC |                 |                                                           |      |       |                 |    |  |  |  |  |

| 高电平输入电压                | V <sub>IH</sub> | ,                                                         | 2    |       | Vcc             | V  |  |  |  |  |

| 低电平输入电压                | V <sub>IL</sub> |                                                           | GND  |       | 0.8             | V  |  |  |  |  |

| 输入钳位电压                 | V <sub>CL</sub> | I <sub>CL</sub> =-18mA                                    |      | -0.86 | -1.5            | V  |  |  |  |  |

| 输入电流                   | I <sub>IN</sub> | V <sub>IN</sub> =0V 或 3.6V                                | -200 | ±100  | 200             | μΑ |  |  |  |  |

|                        |                 | MS1224 LVCMOS/LVTTL DC                                    | 1    | T     | T               |    |  |  |  |  |

| 高电平输入电压                | V <sub>IH</sub> |                                                           | 2    |       | Vcc             | V  |  |  |  |  |

| 低电平输入电压                | VIL             |                                                           | GND  |       | 0.8             | V  |  |  |  |  |

| 输入钳位电压                 | V <sub>CL</sub> | I <sub>CL</sub> =-18mA                                    |      | -0.62 | -1.5            | V  |  |  |  |  |

| 输入电流                   | lin             | V <sub>IN</sub> =0V 或 3.6V                                | -200 |       | 200             | μΑ |  |  |  |  |

| 高电平输出电压                | V <sub>OH</sub> | I <sub>OH</sub> =-5mA                                     | 2.2  | 3     | V <sub>CC</sub> | V  |  |  |  |  |

| 低电平输出电压                | Vol             | I <sub>OL</sub> =5mA                                      | GND  | 0.25  | 0.5             | V  |  |  |  |  |

| 输出短路电流                 | los             | V <sub>OUT</sub> =0V                                      | -15  | -47   | -85             | mA |  |  |  |  |

| 高阻输出电流                 | l <sub>oz</sub> | PWRDN/REN=0.8V,                                           | -10  | ±1    | 10              | μΑ |  |  |  |  |

|                        | 102             | Vouт=0V 或 Vcc                                             | -10  | -1    | 10              | μΛ |  |  |  |  |

|                        |                 | MS1023 LVDS DC                                            | 1    | T     |                 |    |  |  |  |  |

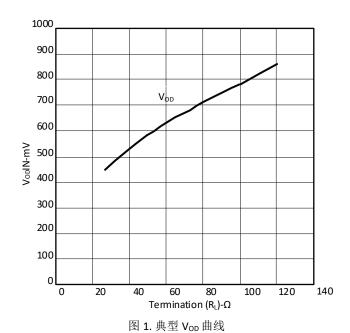

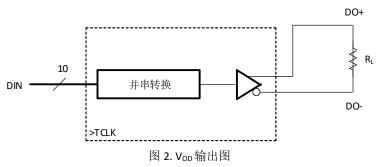

| 差分输出电压                 | V <sub>OD</sub> | R <sub>L</sub> =27Ω,见图 1,2                                | 350  | 450   |                 | mV |  |  |  |  |

| 差分输出抖动电压               | $\Delta V_{OD}$ |                                                           |      |       | 35              | mV |  |  |  |  |

| 失调电压                   | Vos             |                                                           | 1.1  | 1.2   | 1.3             | V  |  |  |  |  |

| 失调抖动电压                 | ΔVos            |                                                           |      | 4.8   | 35              | mV |  |  |  |  |

| 短路输出电流                 | los             | D <sub>O</sub> =0V,D <sub>INx</sub> =high, PWRDN/REN=2.4V |      | -10   | -90             | mA |  |  |  |  |

| 高阻输出电流                 | loz             | PWRDN/REN=0.8V,Do=0V 或 Vcc                                | -10  | ±1    | 10              | μΑ |  |  |  |  |

| 掉电输出电流                 | lox             | V <sub>cc</sub> =0V,D <sub>o</sub> =0V 或 3.6V             | -20  | ±1    | 25              | μΑ |  |  |  |  |

| 输出单端电容                 | Co              |                                                           |      |       | 1±20%           | pF |  |  |  |  |

|                        |                 | MS1224 LVDS DC                                            | 1    | T     |                 |    |  |  |  |  |

| 差分阈值高电压                | V <sub>TH</sub> | V <sub>CM</sub> =1.1V                                     |      |       | 50              | mV |  |  |  |  |

| 差分阈值低电压                | V <sub>TL</sub> |                                                           | -50  |       |                 | mV |  |  |  |  |

| 参数          | 符号                | 测试                                         | 条件       | 最小值 | 典型值   | 最大值  | 单位 |

|-------------|-------------------|--------------------------------------------|----------|-----|-------|------|----|

| 46.2.1.37   |                   | V <sub>IN</sub> =2.4V, V <sub>CC</sub> =0V | / 或 3.6V | -10 | ±1    | 15   |    |

| 输入电流        | I <sub>IN</sub>   | V <sub>IN</sub> =0V, V <sub>CC</sub> =0V J | 或 3.6V   | -10 | ±0.05 | 10   | μΑ |

| 输入单端电容      | Cı                |                                            |          |     | 0.5±  | ±20% | pF |

|             |                   | MS1023 ☐                                   | 二作电流     |     |       |      |    |

|             |                   | R <sub>L</sub> =27Ω,                       | f=10MHz  |     | 20    | 25   | mA |

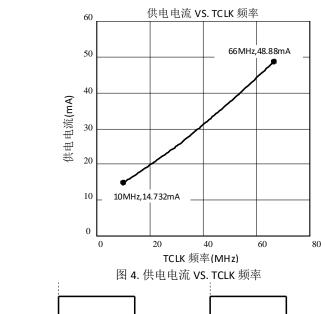

| 串化器供电电流最坏情况 | Iccd              | 见图 3 f=80MHz                               |          |     | 65    | 80   |    |

| 供电电流        | Iccxd             | PWRDN=0.8V                                 |          |     | 200   | 500  | μΑ |

|             |                   | MS1224 <b>∃</b>                            | 作电流      |     |       |      |    |

|             |                   | C <sub>L</sub> =15pF                       | f=10MHz  |     | 15    | 35   | mA |

| 解串器供电电流最坏情况 | I <sub>CCR</sub>  | 见图 5                                       | f=80MHz  |     | 90    | 105  |    |

| 解串器掉电模式供电电流 | I <sub>CCXR</sub> | PWRDN=0.8V, RE                             | N=0.8V   |     | 0.36  | 1    | mA |

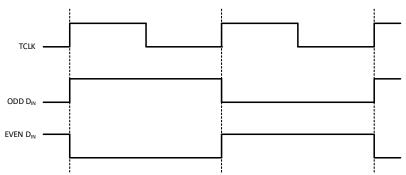

图 3. 最坏情况串化器 Icc 测试模式

图 4. 供电电流 VS. TCLK 频率

ODD Rour

EVEN Rour

图 5. 最坏情况解串器 Icc 测试模式

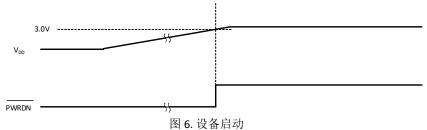

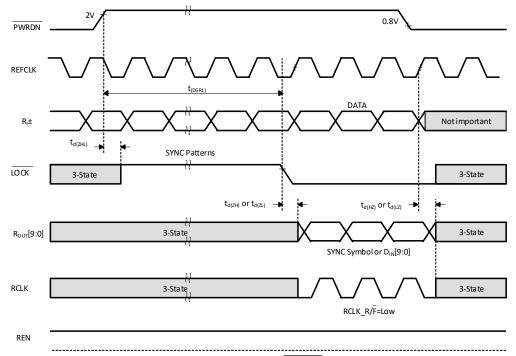

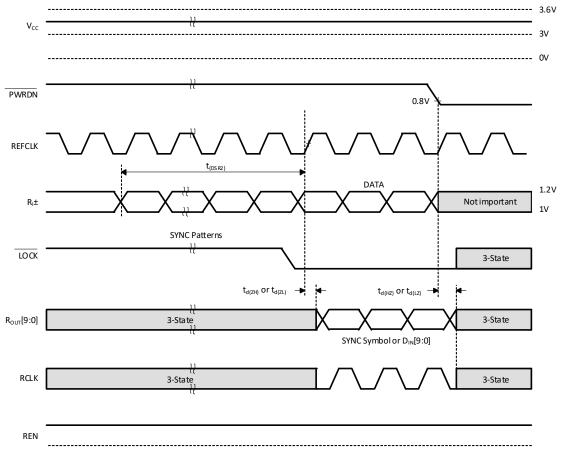

#### 设备启动过程

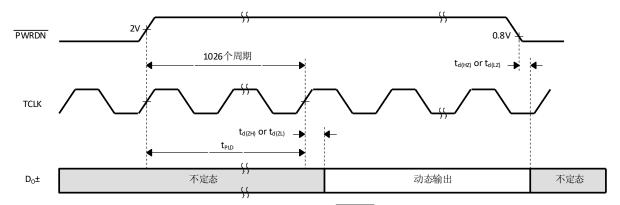

图 6 表明了在串化器和解串器中,PWRDN一直保持逻辑 0,直到电源供电至少达到 3V。

#### 串化器中 TCLK 的时序要求

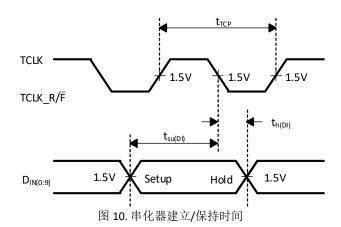

| 参数        | 符号                  | 测试条件 | 最小值   | 典型值  | 最大值  | 单位  |  |  |

|-----------|---------------------|------|-------|------|------|-----|--|--|

| 时钟周期      | t <sub>TCP</sub>    |      | 15.15 | Т    | 100  | ns  |  |  |

| 时钟高电平时间   | t <sub>TCIH</sub>   |      | 0.4T  | 0.5T | 0.6T | ns  |  |  |

| 时钟低电平时间   | t <sub>TCIL</sub>   |      | 0.4T  | 0.5T | 0.6T | ns  |  |  |

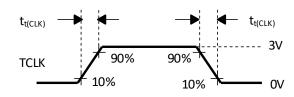

| TCLK 边沿时长 | t <sub>t(CLK)</sub> | 见图 7 |       | 3    | 6    | ns  |  |  |

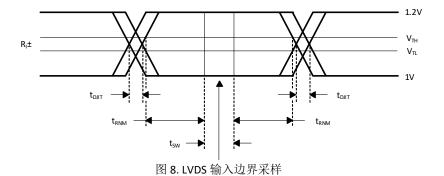

| TCLK 输入抖动 | t <sub>JIT</sub>    | 见图 8 |       |      | 150  | ps  |  |  |

| 频率容差      | Ft                  |      | -100  |      | +100 | ppm |  |  |

图 7. 串化器输入时钟传输时间

串化器转换特性

使用前面提出的工作条件(除给出的测试条件以外)

| 参数       | 符号                  | 测试条件                                            | 最小值 | 典型值  | 最大值 | 单位 |

|----------|---------------------|-------------------------------------------------|-----|------|-----|----|

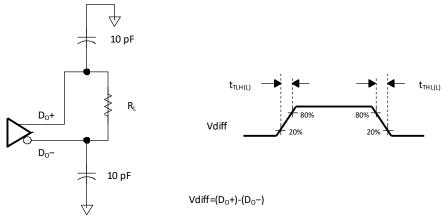

| 上升沿转换时间  | t <sub>TLH(L)</sub> | R <sub>L</sub> =27Ω,C <sub>L</sub> =10pF 到 GND, |     | 0.2  | 0.4 | ns |

| 下降沿转换时间  | t <sub>LTH(L)</sub> | 见图 9                                            |     | 0.25 | 0.4 | ns |

| 数据建立时间   | t <sub>su(DI)</sub> |                                                 | 0.5 |      |     | ns |

| 数据保持时间   | t <sub>su(DI)</sub> | 见图 10                                           | 4   |      |     | ns |

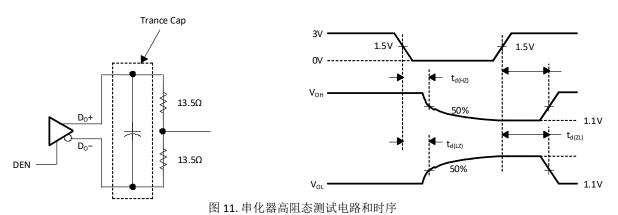

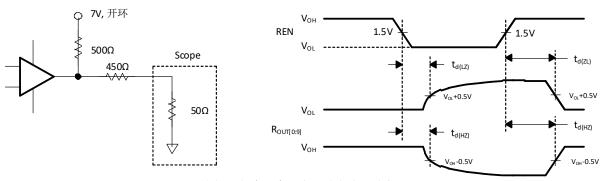

| 高-高阻延时   | t <sub>d(HZ)</sub>  |                                                 |     | 2.5  | 5   |    |

| 低-高阻延时   |                     | R <sub>L</sub> =27Ω,C <sub>L</sub> =10pF 到 GND, |     | 2.5  | 5   |    |

| 高-高阻-高延时 | t <sub>d(ZH)</sub>  | 见图 11,12                                        |     | 5    | 10  | ns |

| 高-高阻-低延时 | t <sub>d(ZL)</sub>  |                                                 |     | 6.5  | 10  |    |

| 参数           | 符号                  | 测试条件                                           | 最小值                 | 典型值                 | 最大值                 | 单位 |

|--------------|---------------------|------------------------------------------------|---------------------|---------------------|---------------------|----|

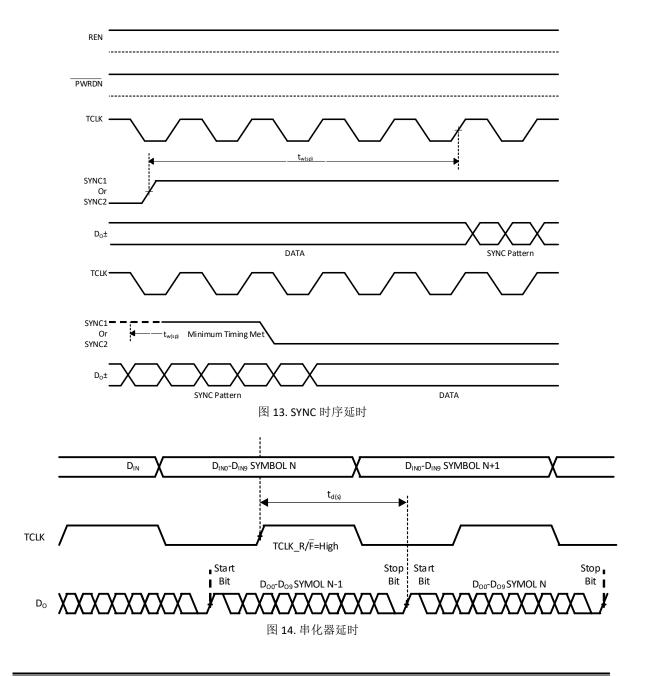

| SYNC 脉冲持续时间  | t <sub>w(SPW)</sub> |                                                | 6×t <sub>TCP</sub>  |                     |                     | ns |

| 串化器 PLL 锁定时间 | t <sub>(PLD)</sub>  | 见图 13                                          | 1026                | 5×t <sub>TCP</sub>  |                     | ns |

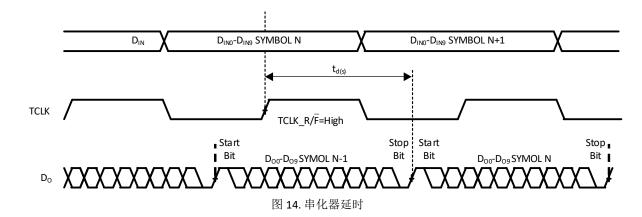

| 串化器延时        | t <sub>d(S)</sub>   | 见图 14                                          | t <sub>TCP</sub> +1 | t <sub>TCP</sub> +2 | t <sub>TCP</sub> +3 | ns |

|              | _                   |                                                |                     |                     | 230                 |    |

| 绝对抖动幅度       | t <sub>DJIT</sub>   | R <sub>L</sub> =27Ω,C <sub>L</sub> =10pF 到 GND |                     |                     | 150                 | ps |

| 随机抖动幅度       | t <sub>RJIT</sub>   | R <sub>L</sub> =27Ω,C <sub>L</sub> =10pF 到 GND |                     | 10                  | 9                   | ps |

图 9. 串化器 LVDS 输出负载和传输时间

图 12. 串化器 PLL 锁定时间和 PWRDN高阻态延时

## 解串器中 REFCLK 时序要求

使用前面提出的工作条件(除给出的测试条件以外)

| 参数          | 符号                 | 测试条件 | 最小值   | 典型值 | 最大值  | 单位  |

|-------------|--------------------|------|-------|-----|------|-----|

| REFCLK 周期   | t <sub>RFCP</sub>  |      | 15.15 | Т   | 100  | ns  |

| REFCLK 占空比  | t <sub>RFDC</sub>  |      | 30    | 50  | 70   | %   |

| REFCLK 边沿时长 | t <sub>t(RF)</sub> |      |       | 3   | 6    | ns  |

| 频率容差        | Ft                 |      | -100  |     | +100 | ppm |

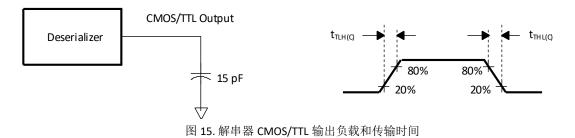

#### 解串器转换特性

| 参数         | 符号                  | 测试条件                                              | 引脚/频率                                  | 最小值                             | 典型值                     | 最大值                              | 单位 |

|------------|---------------------|---------------------------------------------------|----------------------------------------|---------------------------------|-------------------------|----------------------------------|----|

| 接收器输出时钟周期  | t <sub>(RCP)</sub>  | t <sub>(RCP)</sub> =t <sub>(TCP)</sub> ,<br>见图 14 | RCLK                                   | 15.15                           |                         | 100                              | ns |

| 低-高转换时间    | t <sub>TLH(C)</sub> | CL=15pF,                                          | R <sub>OUTO</sub> -R <sub>OUT9</sub> , |                                 | 1.2                     | 2.5                              | ns |

| 高-低转换时间    | t <sub>THL(C)</sub> | 见图 15                                             | LOCK ,RCLK                             |                                 | 1.1                     | 2.5                              | ns |

| , , ,      |                     | 室温,3.3V,                                          | 10MHz                                  | 1.75×t <sub>(RCP)</sub><br>+4.2 |                         | 1.75×t <sub>(RCP)</sub><br>+12.6 | ns |

| 解串器延时      | t <sub>d(D)</sub>   | 见图 16                                             | 80MHz                                  | 1.75×t <sub>(RCP)</sub><br>+7.4 |                         | 1.75×t <sub>(RCP)</sub><br>+9.7  |    |

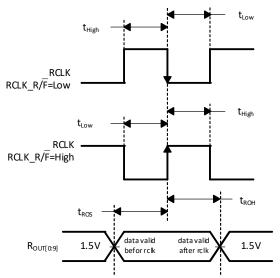

| 在 RCLK 之前  | t <sub>(ROS)</sub>  |                                                   | RCLK 10MHz                             | 0.4×t <sub>(RCP)</sub>          | 0.5×t <sub>(RCP)</sub>  |                                  |    |

| ROUTX 数据有效 |                     |                                                   | RCLK 80MHz                             | 0.4×t <sub>(RCP)</sub>          | 0.5×t <sub>(RCP)</sub>  |                                  | ns |

| 在 RCLK 之后  | t <sub>(ROH)</sub>  | 见图 17                                             | 10MHz                                  | -0.4×t <sub>(RCP)</sub>         | -0.5×t <sub>(RCP)</sub> |                                  |    |

| ROUTX 数据有效 |                     |                                                   | 80MHz                                  | -0.4×t <sub>(RCP)</sub>         | -0.5×t <sub>(RCP)</sub> |                                  |    |

| 时钟占空比      | t <sub>(RDC)</sub>  |                                                   |                                        | 40                              | 50                      | 60                               | %  |

| 高-高阻延时     | t <sub>d(HZ)</sub>  |                                                   |                                        |                                 | 6.5                     | 8                                |    |

| 低-高阻延时     | t <sub>d(LZ)</sub>  |                                                   |                                        |                                 | 4.7                     | 8                                | ns |

| 高阻-高延时     | t <sub>d(HR)</sub>  | 见图 18                                             | R <sub>ОUТ0</sub> -R <sub>ОUТ9</sub>   |                                 | 5.3                     | 8                                |    |

| 高阻-低延时     | t <sub>d(ZL)</sub>  |                                                   |                                        |                                 | 4.7                     | 8                                |    |

| 参数      | 符号                   | 测试条件   | 引脚/频率 | 最小值 | 典型值  | 最大值                   | 单位 |

|---------|----------------------|--------|-------|-----|------|-----------------------|----|

|         |                      |        | 10MHz |     |      | 850×t <sub>RFCP</sub> |    |

| 解串器 PLL | t <sub>(DSR1)</sub>  |        | 80MHz |     |      | 850×t <sub>RFCP</sub> | μs |

| 锁存时间    |                      | 见图 19, | 10MHz |     |      | 2                     |    |

|         | t <sub>(DSR2)</sub>  | 见图 20  | 80MHz |     |      | 0.303                 |    |

| 高阻-高延时  |                      |        |       |     |      |                       |    |

| (启动)    | t <sub>d(ZHLK)</sub> |        | LOCK  |     |      | 3                     | ns |

|         |                      |        | 10MHz |     | 3680 |                       |    |

| 解串器噪声极限 | t <sub>RNM</sub>     | 见图 8   | 80MHz |     | 540  |                       | ps |

Stop Start Bit Bit Stop Start Bit Bit Start Stop Bit Bit | D<sub>00</sub>-D<sub>09</sub>SYMOL N-1 D<sub>00</sub>-D<sub>09</sub> SYMOL N D<sub>00</sub>-D<sub>09</sub> SYMOL N  $t_{\text{\tiny DD}}$ RCLK TCLK\_R/F=high  $\mathbf{R}_{\text{OUT}}$ R<sub>OUTO</sub>-R<sub>OUT9</sub> SYMBOL N+1 R<sub>OUTO</sub>-R<sub>OUT9</sub> SYMBOL N-1  $R_{\text{OUT0}}\text{-}R_{\text{OUT9}}\,\text{SYMBOL}\,\,N$

图 16. 解串器延时

图 17. 解串数据有效输出时序

图 18. 解串器高阻态测试电路及时序

图 19. 解串器 PLL 锁定时序及 PWRDN不定态延时

图 20. 解串器 PLL 在同步过程中的锁定时间

#### 功能描述

MS1023和MS1224是一对10位串化/解串器芯片,可以通过差分底板或双绞线,传输10MHz到80MHz数据。这一对芯片有5种工作状态:初始化模式、同步模式、数据传输模式、掉电模式及高阻传输模式。下面将分节描述每一个工作状态。

#### 初始化模式

在数据传输启动前,必须初始化。初始化涉及串化器的同步和解串器的PLL锁定本地时钟。

当Vcc加到串化器或解串器上,输出响应进入高阻态。同时,芯片内的电源电路使得内部电路失去功能。当Vcc达到2.45V,PLL开始锁定本地时钟。对于串化器,本地时钟是外部时钟源提供的传输时钟(TCLK)。对于解串器,本地时钟必须对应REFCLK脚的输入。当PLL锁定到TCLK,串化器输出保持高阻态。

#### 同步模式

为了接收有效数据,解串器的PLL必须同步到串化器。同步可通过以下两种方式完成:

快速同步: 串化器能够发送特定的SYNC样本信号——由6个1和6个0组成,其值转换由输入时钟速率决定。SYNC样本传输使能解串器,在一个确定的时间帧内锁定到串化器信号。SYNC样本信号传输与否由串化器的SYNC1和SYNC2输入决定。当连续收到有效的SYNC1或SYNC2脉冲(时间宽度超过6个时钟周期),SYNC样本信号将会发送。

当解串器在LVDS输入上检测到边沿传输,它将尝试锁定到内嵌的时钟信息。解串器 LOCK 输出保持高,同时PLL锁定输入数据或来自串化器的SYNC样本信号。当解串器锁定到LVDS数据,LOCK 输出变低。当LOCK 为低,解串器输出开始恢复输入的LVDS数据。一种方法是将解串器 LOCK 输出直接连接到SYNC1或SYNC2。

随机锁定同步:解串器可从数据流中获取时钟,而不需要串化器发送特定的同步模式信号。这允许MS1224工作在开环应用中。重要的是——在工作时,解串器支持热插拔。在开环或热插拔情况下,假定数据流在本质上是随机的。因此,由于锁定时间根据数据流特征而变化,所以准确时间是不可能预知的。当解串器启动,在随机锁定时间上,首先要约束的是输入数据与REFCLK之间的初始相位。

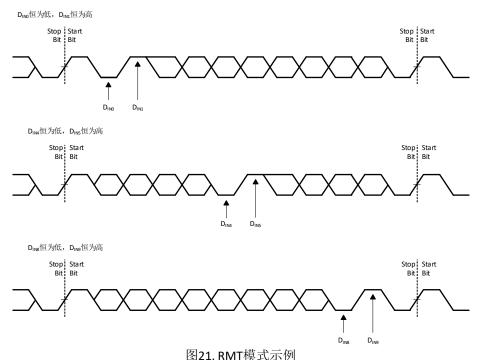

数据流中的数据同样影响锁定时间,如果一个特殊的模式是重复性的,解串器可能进入错误的锁定——把输入数据模式误认为起始/终止位。这被认为是重复性多级传输(RMT),见图21的RMT示例。当在多个周期内,每个时钟周期里发生多次低-高电平转换时,将形成RMT。在最坏情况中,解串器可能锁定数据模式而不是时钟。解串器里的电路可以检测潜在的错误时钟。通过检测,电路防止(输出)变为动态,直到潜在的错误时钟改变。观察到RMT模式仅仅影响到解串器锁定时间,同时一旦解串器锁定,RMT模式不会影响解串器状态(即使每个周期内发生相同数据边界)。解串器不会进入锁定,直到它在同一位置找到1个特殊的/4个连续时钟的数据边界(STOP/START bits)。

解串器保持锁定,直到在连续四个时钟周期内,都检测不到相同的数据边界(STOP/START bits)。然后,解串器解除锁定和寻找新的数据边界(STOP/START bits)。在同步缺失的情况下,LOCK 输出置高电平,输出(包括RCLK)进入高阻态。用户系统应监控LOCK 以防同步缺失。当检测到锁定缺失,如果在特定的时间内无法复位锁定,可发送重新同步的SYNC样本信号。然而,解串器可以锁定随机数据(前面已提及)。

#### 数据传输模式

在初始化和同步完成之后,串化器从 DINO-DIN9 输入口接收并行数据。串化器使用时钟输入来锁定输入数据。TCLK\_R/F引脚选择串化器使用哪个边沿来忽略输入数据。如果任一个 SYNC 输入为高超过 6 个 TCLK 周期,无论选择哪个时钟边沿,都会忽略 DINO-DIN9 数据并且会发送 1026 个时钟周期的 SYNC 样本信号。

在决定了使用的时钟边沿之后,一个起始位和停止位嵌入到每一帧数据的寄存器中。起始位恒为 高,停止位恒为低。在串行数据流中,起始停止位作为嵌入时钟信息。

串化器以 TCLK 的 12 倍频,传输串行数据以及内嵌时钟位(10+2bits)。比如,如果 TCLK 为80MHz,串行速率为80×12 = 960Mbps。由于仅有 10 位输入数据,有效数据速率应为 10 倍的 TCLK 频率。例如,如果时钟为 80MHz,有效数据速率为 80×10 = 800Mbps。而提供 TCLK 的数据源要求在10MHz 至 80MHz 之间。

一旦解串器同步到串化器,LOCK 脚输出低。解串器锁定到嵌入时钟,同时使用该时钟来恢复串化数据。ROUT 数据在LOCK 低时有效,因此 ROUTO-ROUT9 有效。在 RCLK 边沿,忽略 ROUTO-ROUT9。特殊的 RCLK 极性将由 RCLK\_R/F输入决定。在 80MHz 时钟时,ROUTO-ROUT9 、LOCK 、RCLK 输出可以驱动三端 CMOS 输入门(3 个引脚接电容的总和为 15pF)。

#### 掉电模式

当没有传输需求,可以使用掉电模式。串化器和解串器的掉电状态是一种低功耗的睡眠模式,可以减小功耗。当 PWRDN 和 DEN 被置低时,解串器进入掉电模式。当 PWRDN 为低时,串化器进入掉电模式。在掉电模式下,锁相环和输出进入高阻状态,禁用负载电流并且供电电流减少到微安级(μA级)。要退出掉电模式,必须驱动 PWRDN 为高。

在串化器和解串器之间的有效数据交换恢复之前,必须再次初始化和再次同步。串化器的初始化耗时 1026 个 TCLK 周期。解串器初始化,同时驱动LOCK 为高,直至锁定到 LVDS 时钟。

#### 高阻模式

当 DEN 被置低时,串化器进入高阻模式。这将使所有输出脚(DO+和 DO-)进入高阻状态。当驱动 DEN 为高,串化器恢复到先前的状态,同时其他所有控制引脚保持静态 (SYNC1,SYNC2, $\overline{PWRDN}$ ,TCLK\_R/F)。当 REN 脚被置低时,解串器进入高阻模式。相应地,接收芯片的输出脚(ROUT0-ROUT9)和 RCLK 进入高阻状态。 $\overline{LOCK}$  保持有效,用来跟踪 PLL 的状态。

| 输入    |     | 输出                     |                   |                     |  |

|-------|-----|------------------------|-------------------|---------------------|--|

| PWRDN | REB | ROUT(0:9) <sup>1</sup> | LOCK <sup>2</sup> | RCLK <sup>1,3</sup> |  |

| Н     | Н   | Z                      | Н                 | Z                   |  |

| Н     | Н   | Active                 | L                 | Active              |  |

| L     | ×   | Z                      | Z                 | Z                   |  |

| Н     | L   | Z                      | Active            | Z                   |  |

表 1. 串并转换器真值表

#### 注:

- 1. 当LOCK 置高, ROUT 和 RCLK 为不定态。

- 2. LOCK 输出反映解串器处理输入数据流的状态。

- 3. 如果解串器锁定,RCLK为 Active 表明 RCLK 在工作。与 ROUT 相关的 RCLK 时序由 RCLK\_R/F决定。

#### MS1224 偏置故障保护

MS1224 有±50mV 的输入阈值灵敏度,这允许 MS1224 有更大的差分噪声极限输入。然而,在接收器输入没有被动地驱动的情况下,MS1224 增加的灵敏度可能会把噪声当作输入信号并且引起无法预料的锁定。这种情况可能会发生在输入悬空时。MS1224 有片上故障保护电路,驱动输入和LOCK 信号为高。故障保护电路的响应时间取决于内部连接电路的特性。

# 典型应用图

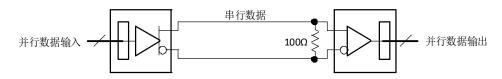

图 22 单终端点对点连接

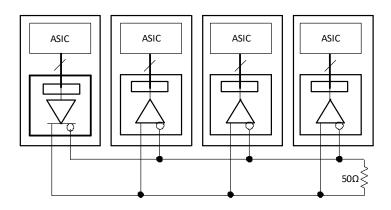

图 23. 多路连接配置

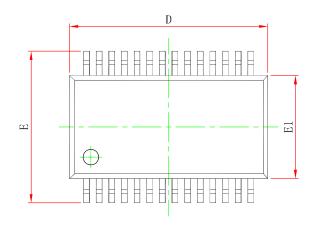

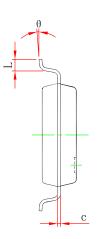

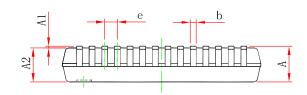

# 封装外形图

#### SSOP28

| 符号 | 尺寸(   | (毫米)   | 尺寸(英寸)   |       |  |

|----|-------|--------|----------|-------|--|

|    | 最小    | 最大     | 最小       | 最大    |  |

| А  | -     | 2.000  | ı        | 0.079 |  |

| A1 | 0.050 | ı      | 0.002    | -     |  |

| A2 | 1.650 | 1.850  | 0.065    | 0.073 |  |

| b  | 0.220 | 0.380  | 0.009    | 0.015 |  |

| С  | 0.090 | 0.250  | 0.004    | 0.010 |  |

| D  | 9.900 | 10.500 | 0.390    | 0.413 |  |

| E  | 7.400 | 8.200  | 0.291    | 0.323 |  |

| E1 | 5.000 | 5.600  | 0.197    | 0.220 |  |

| e  | 0.65  | OBSC   | 0.026BSC |       |  |

| L  | 0.550 | 0.950  | 0.022    | 0.037 |  |

| θ  | 0°    | 8°     | 0°       | 8°    |  |

# 印章与包装规范

1. 印章内容介绍

产品型号: MS1023、MS1224

生产批号: XXXXXX

2. 印章规范要求

采用激光打印,整体居中且采用 Arial 字体。

3. 包装规范说明

| 型号     | 封装形式   | 只/卷  | 卷/盒 | 只/盒  | 盒/箱 | 只/箱   |

|--------|--------|------|-----|------|-----|-------|

| MS1023 | SSOP28 | 2500 | 1   | 2500 | 8   | 20000 |

| MS1224 | SSOP28 | 2500 | 1   | 2500 | 8   | 20000 |

#### 声明

- 瑞盟保留说明书的更改权,恕不另行通知!客户在下单前应获取最新版本资料,并验证相关信息 是否完整。

- 在使用瑞盟产品进行系统设计和整机制造时,买方有责任遵守安全标准并采取相应的安全措施, 以避免潜在失败风险可能造成的人身伤害或财产损失!

- 产品提升永无止境,本公司将竭诚为客户提供更优秀的产品!

#### MOS电路操作注意事项

静电在很多地方都会产生,采取下面的预防措施,可以有效防止 MOS 电路由于受静电放电的影响而引起的损坏:

- 1、操作人员要通过防静电腕带接地。

- 2、设备外壳必须接地。

- 3、装配过程中使用的工具必须接地。

- 4、必须采用导体包装或抗静电材料包装或运输。

+86-571-89966911

杭州市滨江区伟业路 1 号 高新软件园 9 号楼 701 室

http://www.relmon.com